PART15조합 논리 회로

실험 4 :가감산기(Adder/ Subtracter)

이론

반가산기(Half Adder)

반가산기는 2개의 2진 입력과 2개의 2진 출력으로 구성된다. 입력 변수들은 피가수와 가수를 나타내고 출력 변수들은 합과 캐리를 의미한다. 일반적으로 두 입력을 x, y로, 출력을 S와 C로 부른다. 입력과 출력에 대한 진리표는 표 15-9와 같다.

C는 입력들이 둘 다 1일 때만 1이 된다. S는 입력이 둘 중 하나가 1일 때만 1이 된다. 두 출력에 대한 단순한 부울 함수들은 진리표로부터 직접 얻을 수 있다. 곱셈의 단순화된 합은 다음과 같다.

이것을 논리도로 표시한 것이 그림 15-11이며 반가산기에 대한 다른 4가지 논리도들도 그림 15-11에 있다. 이것들은 모두 입력과 출력의 작동에 관한 한 똑같은 결과를 산출한다. 이것을 볼 때 우리는 이와 같은 간단한 조합 논리 함수를 제작할 때조차 여러 가지 다양한 선택이 있을 수 있음을 알 수 있다.

그림 15-11(a)는 반가산기를 곱의 합으로 구현한 것이며, (b)는 합의 곱으로 구현한 것이다.

(c)는 S가 x와 y의 Exclusive-OR이라는 사실에서 얻어진다. S의 보수는 x와 y의 동치이다.

그런데 C=xy이므로

(d)에서 C를 합의 곱으로 표현하면 다음과 같다.

반가산기는 (e)에서처럼 Exclusive-OR 게이트와 AND 게이트로 실현할 수 있다.

전가산기(Full Adder)

전가산기는 3개의 입력 비트들의 합을 계산하는 조합회로이다. 전가산기는 3개의 입력과 2개의 출력으로 구성된다. x와 y로 표시된 입력 변수들은 더해질 현재 위치의 두 비트이며, z로 표시된 세 번째 입력 변수는 바로 전 위치로부터의 캐리이다. 3개의 비트를 더할 때 합은 0부터 3까지 나올 수 있고, 2와 3을 2진수로 표시하는 데 2개의 디지트가 요구되므로 2개의 출력이 필요하다. 두 출력 중 합에 대해서는 S라는 기호로, 캐리에 대해서는 C라는 기호로 표시한다. 3개의 비트의 합을 계산하여 앞의 디지트는 출력 캐리 C가 되며, 뒤의 디지트가 S로 표시된다. 전가산기의 진리표는 그림 15-12과 같다.

3개의 입력 변수들이 가질 수 있는 모든 가능한 1과 0들의 조합에 대해서 2개의 출력 변수는 1 또는 0의 값을 가진다. 모든 입력들이 0일 때 출력은 0 이 된다. 출력 S는 1개 또는 3개의 입력들이 1일 때 1이 된다.

조합 회로의 입출력 비트들은 문제의 여러 단계에서 다르게 해석할 수 있다. 입력선의 2진 신호는 산술적으로 더해져 2 디지트 합을 출력선에 산출하는 비트로 간주한다.

반면에 진리표로 표현할 때나 논리 게이트로 회로를 구성할 때에 앞 문장에서와 동일한 2진 값을 부울 함수의 변수로 볼 수 있다. 이렇게 이 회로에서 쓰이는 비트들이 2가지의 다른 해석을 할 수 있다는 것을 인식하는 것은 중요한 일이다.

전가산기 회로의 입출력 논리 관계는 각 출력 변수에 대해 하나의 부울 함수가 대응되므로 2개의 부울 함수로 표현될 수 있다. 각 부울 함수를 단순화시키기 위해 맵이 하나씩 필요하다. 각 맵은 출력이 세 입력 변수들의 함수이므로 8개의 사각형들로 구성된다. 그림 15-13에 있는 2개의 맵들은 두 출력 함수들을 각각 단순화하는데 사용한다. 각 맵의 사각형 내에 표시된 1은 진리표로부터 직접 얻을 수 있다. 출력 S의 경우 1로 표시한 사각형들은 인접한 사각형과 결합할 수 없으므로 더 이상 단순화시킬 수 없다. 출력 C는 단순화되어져 6개의 문자로 된 표현을 얻는다. 곱의 합으로 전가산기의 논리도가 그림 15-14에 있다. 이것은 다음 부울 함수 표현을 사용한 것이다.

전가산기에 대한 다른 구성을 개발할 수 있다. 합의 적으로 표현할 경우 그림 15-14과 같은 수의 게이트를 사용하지만 AND 게이트와 OR 게이트의 수가 서로 바뀐다.

전가산기는 그림 15-15에서처럼 2개의 반가산기와 하나의 OR 게이트로 구현할 수 있다. 두 번째 반가산기의 출력 S는 첫 번째 반가산기의 출력과 z를 Exclusive-OR한 것이다. S와 C는 다음과 같이 부울 함수로 표현할 수 있다.

반감산기 (Half Subtracter)

반감산기는 2개의 비트들을 빼서 그 차를 산출하는 조합회로이다. 이 회로는 1을 빌렸는지를 나타내는 또 하나의 출력을 가진다. x는 피감산 비트를 표시하는 데 사용하고 y는 감산 비트를 표시하는 데 사용한다. x-y를 수행하기 위해 우리는 x와 y의 상대적인 크기를 살펴보아야 한다. x≥y이면 다음 세 경우가 가능하다. 0-0=0, 1-0=1, 그리고 1-1=0. 이 결과를 차 비트(difference bit)라 부른다. 만일 x<y인 경우, 즉 0-1일 때에는 바로 앞 자릿수로부터 1을 빌어야만 한다. 빌린 1은 2진수에서 2와 같으므로 감산수 비트에 더해져 결국 2-1=1이 된다. 반감산기는 2개의 출력이 필요한데, 하나는 차를 생성하여 기호 D로 표시하고 또 다른 하나는 기호 B로 받아내림(borrow) 표시하여, 앞 위치의 디지트로부터 1이 빌어지는지를 표시한다. 반감산기에 대한 진리표는 그림 15-16와 같다.

출력 B는 x≥y이면 0이고, x=0, y=1에 대해서만 1이 된다. 출력 D는 산술연산 2B+x-y의 결과이다. 반감산기 두 출력에 대한 부울 함수들은 진리표에서 직접 구할 수 있다.

D에 관한 논리가 반가산기에서 S에 관한 논리와 동일하다.

전감산기(Full Subtracter)

전감산기는 바로 전 낮은 단 위치의 디지트에 빌려 준 1을 고려하면서 두 비트들의 뺄셈을 수행하는 조합회로이다. 이 회로는 3개의 입력과 2개의 출력을 가진다. x, y, z는 각각 피감수, 감수, 그리고 전 자릿수로부터의 빌림(borrow)을 표시하는데 사용되는 출력기호이다. 전감산기의 진리표는 그림 15-17과 같다.

3개의 입력 변수들이 가질 수 있는 모든 가능한 1과 0들의 조합에 대해 두 출력 변수의 값은 x-y-z의 결과에 따라서 "1"또는 "0"으로 결정된다. 입력 빌림(z)이 0이면 반감산기와 동일하게 된다. x=0, y=0, z=1인 경우 바로 앞 디지트로부터 1을 빌어 와야 한다. 그 경우 2가 x에 가해지므로 2-0-1=1이 되어 D=1이고 이 때 빌림이 있으므로 B도 1이 된다. x=0, yz=11일 때도 앞 디지트로부터 1을 빌어야 하므로 B=1이고, x는 2가 더해져 D는 2-1-1=0에 의해 0이 된다. x=1, yz=01일 때 x-y-z=0이므로 B=0, D=0이 된다. 마지막으로 x=1, yz=11이면 앞 디지트로부터 1을 빌어 x는 2가 더해져 3이 되므로 D=1, B=1이 된다.

전감산기의 두 출력에 대한 부울 함수들은 그림15-18의 맵에 있다. 이것을 단순화하여 적의 합으로 나타내면 다음과 같다.

전가산기의 출력 S와 전 감산기의 출력 D는 동일하며 전감산기의 출력 B는, x를 x로 대치하면 동일하게 된다는 사실이 흥미있는 일이다. 따라서 x의 보수를, 캐리를 산출하는 게이트에 적용하면 간단히 전가산기를 전감산기로 바꿀 수 있다.

실험 과정

1. M-15의 회로-4에서 4f-4g 단자를 연결하여 그림 15-19와 같이 반가산기를 구성한다.

2. 입력 A, B가 표 15-6과 같을 때, 출력 Sum(4l)과 Carry(4h)를 해당란에 기록한다.

tab1실험 15-4.1 가산기/감산기(Adder/Subtracter)회로 실험 (M15의 Circuit-4 회로)

반가산기(Half Adder) 회로 : M-15의 Circuit-4에서 그림 15-19과 같이 반가산기를 구성한다

1.결선 방법

1.회로 결선

반가산기 입력 : M15의 Circuit-4에서 전면 패널 Digital Output의 Q0 단자와 4a 단자 간, Q2 단자와 4b 단자 간을 적색선으로 연결하고, COM 단자와 GND 단자 간을 흑색선으로 연결한다.

Circuit-4에서 4f 단자와 4g 단자 간을 황색선으로 연결한다.

2.전원 결선은 내부적으로 연결되어 있다.

2.결선도

3.측정 방법

- 1입력 A, B가 표 15-7과 같을 때, 출력 합(Sum(4n))과 자리올림(Carry(4h))의 해당란에 기록한다.

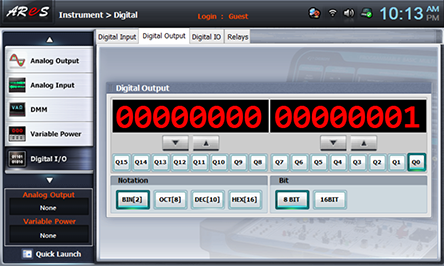

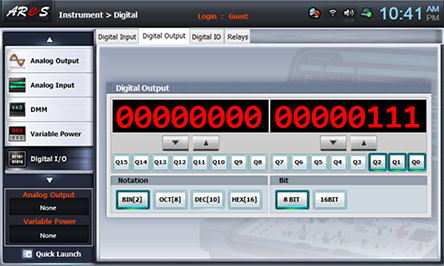

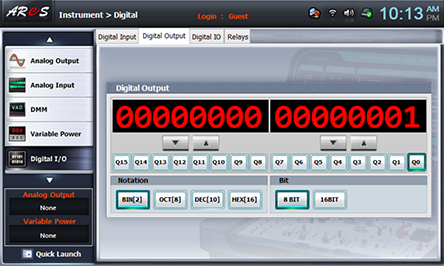

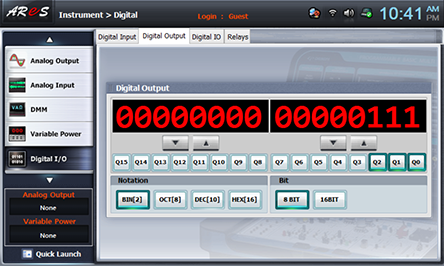

Touch LCD 패널에서 digital i/o 를 선택하고, Digital Output 탭을 클릭한 다음 Bit 란에서 를 선택하고, 표 15-7의 입력데이터와 같이 Q0, Q1을 클릭하여 적색 LED(자리올림)와 녹색 LED(합)의 결과를 기록한다.(Q0 출력은 반가산기 A 입력, Q1 출력은 반가산기 B에 대응)

4.계산

1. 출력 합(Sum)과 자리올림(Carry)에 대한 논리식을 작성하시오.

전가산기(Full Adder) 회로 : M-15의 Circuit-4에서 그림 15-20과 같이 전가산기를 구성한다

1.결선 방법

1.회로 결선

전가산기 입력 : M15의 Circuit-4에서 전면 패널 Digital Output의 Q0 단자와 4a 단자 간, Q2 단자와 4b 단자 간을 적색선으로 연결하고, COM 단자와 GND 단자 간을 흑색선으로 연결한다./p>

전가산기 Carry 입력 : 전면 패널 Digital Output의 Q2 단자와 4c 단자 간을 적색선으로 연결한다.

Circuit-4에서 4f 단자와 4g 단자 간, 4h 단자와 4i 단자 간, 4l 단자와 4m 단자 간, 4n 단자와 4o 단자 간을 황색선으로 연결한다.

2.전원 결선은 내부적으로 연결되어 있다.

2.결선도

3.측정 방법

- 1입력 A, B, Carry가 표 15-8과 같을 때, 출력 합(Sum(4r))과 자리올림(Carry(4p))을 해당란에 기록한다.

Touch LCD 패널에서 digital i/o 를 선택하고, Digital Output 탭을 클릭한 다음 Bit 란에서 를 선택하고, 표 15-8의 입력데이터와 같이 Q0, Q1, Q2을 클릭하여 적색 LED(Carry)와 녹색 LED(Sum)의 결과를 기록한다.(Q0 출력은 전가산기 A 입력, Q1 출력은 전가산기 B 입력, Q2 출력은 자리올림(Carry) 입력에 대응)

4.계산

1. 출력 합(Sum)과 자리올림(Carry)에 대한 논리식을 작성하시오

반감산기(Half Subtracter) 회로 : M-15의 Circuit-4에서 그림 15-21과 같이 반감산기를 구성한다.

1.결선 방법

1.회로 결선

반감산기 입력 : M15의 Circuit-4에서 전면 패널 Digital Output의 Q0 단자와 4a 단자 간, Q2 단자와 4b 단자 간을 적색선으로 연결하고, COM 단자와 GND 단자 간을 흑색선으로 연결한다.

Circuit-4에서 4d 단자와 4f 단자 간, 4e 단자와 4g 단자 간을 황색선으로 연결한다.

2.전원 결선은 내부적으로 연결되어 있다.

2.결선도

3.측정 방법

- 1입력 A, B가 표 15-9와 같을 때, 출력 차(Differ(4n))와 자리내림(Borrow(4h))을 해당란에 기록한다.

Touch LCD 패널에서 digital i/o 를 선택하고, Digital Output 탭을 클릭한 다음 Bit 란에서 를 선택하고, 표 15-9의 입력데이터와 같이 Q0, Q1을 클릭하여 적색 LED(자리내림)와 녹색 LED(차)의 결과를 기록한다.(Q0 출력은 반감산기 A 입력, Q1 출력은 반감산기 B에 대응)

4.계산

1. 출력 차와 자리내림에 대한 논리식을 작성하시오

전감산기(Full Subtracter) 회로 : M-15의 Circuit-4에서 그림 15-22과 같이 전감산기를 구성한다

1.결선 방법

1.회로 결선

전감산기 입력 : M15의 Circuit-4에서 전면 패널 Digital Output의 Q1 단자와 4a 단자 간, Q2 단자와 4b 단자 간을 적색선으로 연결하고, COM 단자와 GND 단자 간을 흑색선으로 연결한다.

전감산기 자리내림(Borrow) 입력 : 전면 패널 Digital Output의 Q0 단자와 4c 단자 간을 적색선으로 연결한다.

Circuit-4에서 4f 단자와 4d 단자 간, 4g와 4e 단자 간, 4h 단자와 4i 단자 간, 4l 단자와 4j 단자 간, 4m 단자와 4k 단자 간, 4n 단자와 4o 단자 간을 황색선으로 연결한다.

2.전원 결선은 내부적으로 연결되어 있다.

2.결선도

3.측정 방법

- 1입력 A, B, Borrow가 표 15-10과 같을 때, 출력 차(Diffier(4r))와 자리내림(Borrow(4p))를 해당란에 기록한다.

Touch LCD 패널에서 digital i/o 를 선택하고, Digital Output 탭을 클릭한 다음 Bit 란에서 를 선택하고, 표 15-10의 입력데이터와 같이 Q0, Q1, Q2을 클릭하여 적색 LED(자리내림)와 녹색 LED(차)의 결과를 기록한다.(Q0 출력은 자리내림(Borrow) 입력, Q1 출력은 전감산기 A 입력, Q2 출력은 전감산기 B 입력 입력에 대응)

4.계산

1. 출력 차와 자리내림에 대한 논리식을 작성하시오